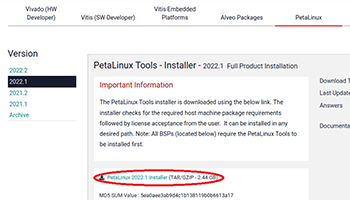

PetalinuxでWavファイルを再生する(2)

Xilinx IPを使いPetalinuxで音声再生する

公開日:2023年7月31日

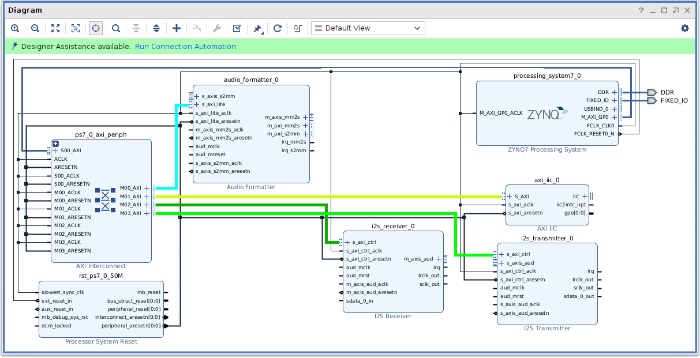

今回は Xilinx社が元々提供している I2S Receiver/I2S Transmitter のIPを組み合わせた、音声再生を目指します。また、Petalinuxから利用する際にデバイスドライバを用意します。

まずはブロックデザインを作ります。

回路規模が大きくなってくると結線先の間違いが多くなるので、注意が必要です。

目次

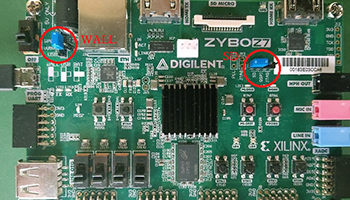

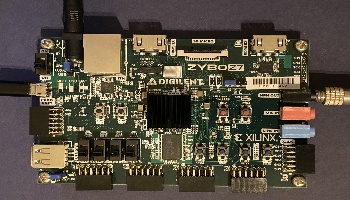

プロジェクト作成

まずは、Zybo Z7-20 用のVivadoプロジェクトを新規作成します。既存プロジェクトから使い回しをすると、余計な設定が残ってしまう場合もあるため、なれないうちは作り直したほうが良いです。

- New Project [Next >]

- Project name: petlainux3 [Next >]

- RTL Project [Next >]

- Boards で digilentinc.com の Zybo Z7-20 を選択 [Next >]

- [Finish]

Zynq7 Processing System

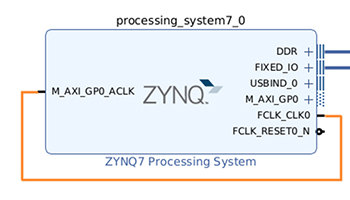

Flow Navigator -> IP INTEGRATOR -> Create Block Design で block design を作成します。

次に ZYNQ7 Prosessing System を追加し、上部に出ている Run Block Automation を押してそのまま [OK] を押します。

Xilinx IPの追加と接続

続いて I2S Receiver, I2S Transmitter, Audio Formatter, AXI IIC を追加します。

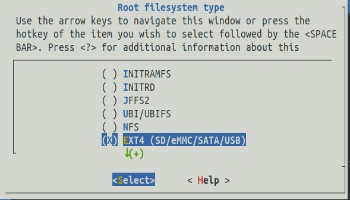

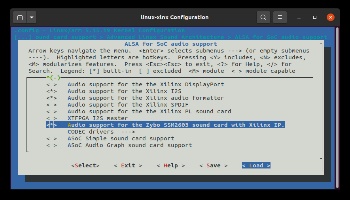

ふたたび Run Block Automation を押し、今度は次のインターフェースのみ選択して [OK] します。

設定1(クリックで拡大)

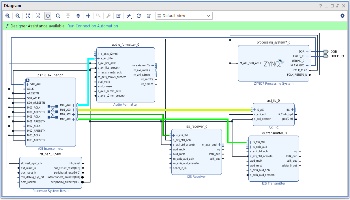

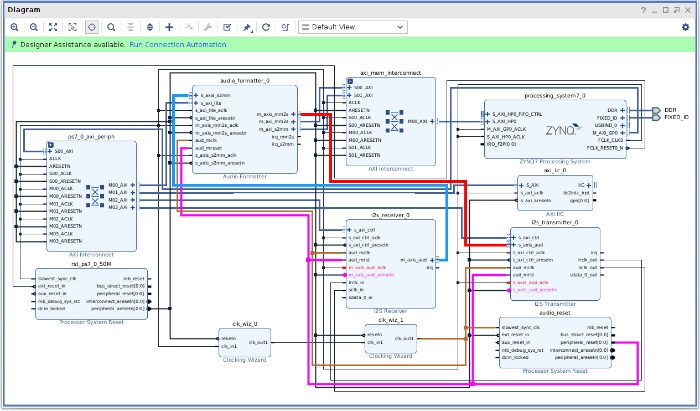

ここまででブロックデザインはこのようになります。

接続先が分かりやすいよう、一部色付けでハイライトさせています。

ワイヤ部分を右クリックして出てくるメニューに Highlight という項目があります。これで色を強調させることが出来て、IPの配置を変えても追従してくれます。ピンやIPに対しても設定できる場合があるので、接続関係の確認に便利な機能です。

ただし、Vivadoプロジェクトを再び起動したときには、ハイライトは失われているので注意が必要です。

ここまでのブロックデザイン(クリックで拡大)

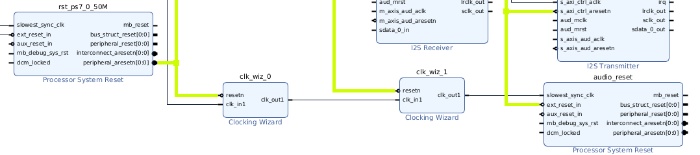

Audio Clock と Processor System Reset

12.288MHz (サンプリングレート 48kHzのマスタクロックとして x256=12.288MHzで動かす) のオーディオクロックの生成と、そのクロックに同期したリセット信号を利用するため、 Processor System Reset を追加します。

まずは Clocking Wizard を二つ追加します。IPカスタマイズウィンドウで、それぞれ次のように変更します。

| 設定 | clk_wiz_0 | clk_wiz_1 |

|---|---|---|

| Output Clocks > Output Freq > Requested | 100.000 | 12.288 |

| Output Clocks > Reset Type | Active Low | Active Low |

| Output Clocks > locked | 無効化 | 無効化 |

つづいて Processor System Reset のIPを追加します。Processor System Reset は、わかりやすいように IP NAME を audio_reset にしておきます。

クロックとリセット信号を接続します。

クロックは ZYNQ:FCLK_CLK0 から順に clk_wiz_0 → clk_wiz_1 → audio_reset:slowest_sync_clk 、リセットは rst_ps7_0_50M_peripheral_aresetn と全て直結します。

下図ではリセットの線が枠外になっていますが、全て同じ信号です。

接続部分(クリックで拡大)

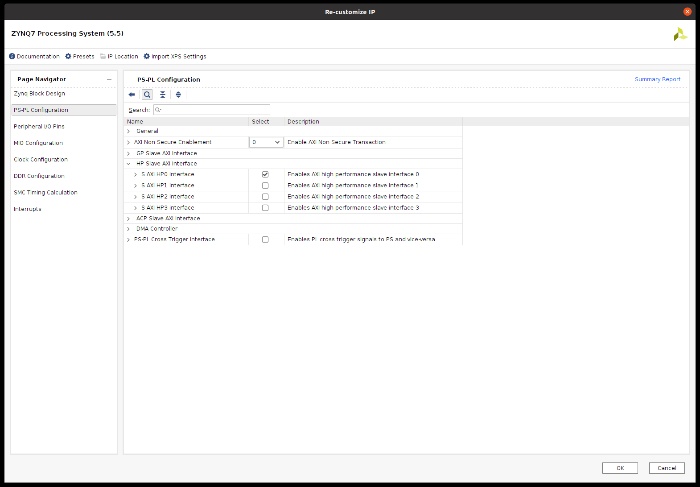

ZYNQ Processor の設定

オーディオ信号の伝送に DMA を使用するため、 ZYNQ Processor で DMA 用に大容量のデータ転送が可能な AXI_HP0 を有効にします。

PS-PL Configuration -> HP Slave AXI Interface -> S AXI HP0 Interface にチェックを入れます。

PSPL_config(クリックで拡大)

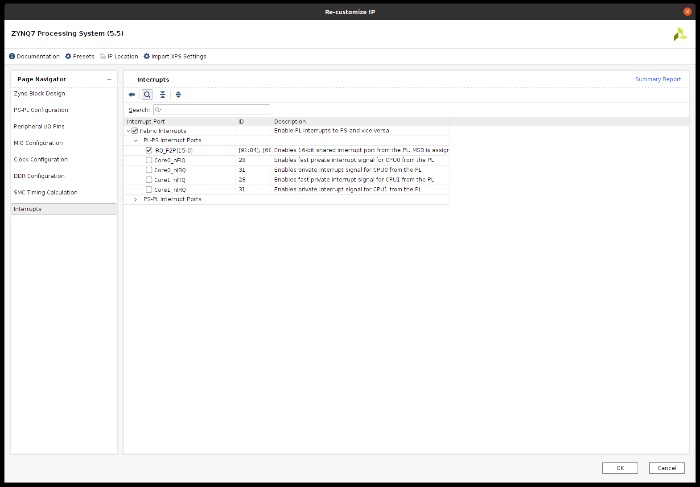

また割込み処理の端子も有効にしておきます。

- Interrupt -> Fabric Interrupts にチェック

- PL-PS Interrupts Ports -> IRQ_F2P[15:0] にチェック

Interrupts(クリックで拡大)

AXI Interconnect (DMA 用)

AXI Interconnect を追加し、 IP NAME を axi_mem_interconnect とします。

今回マスター側は1つで足りるため、IPカスタム画面で Number of Master Interfaces を 1 にしておきます。

Interrupts(クリックで拡大)

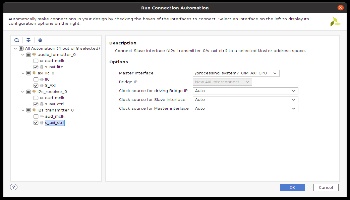

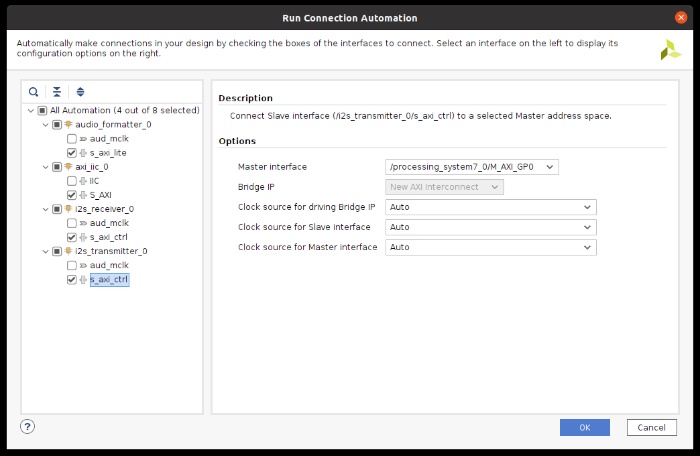

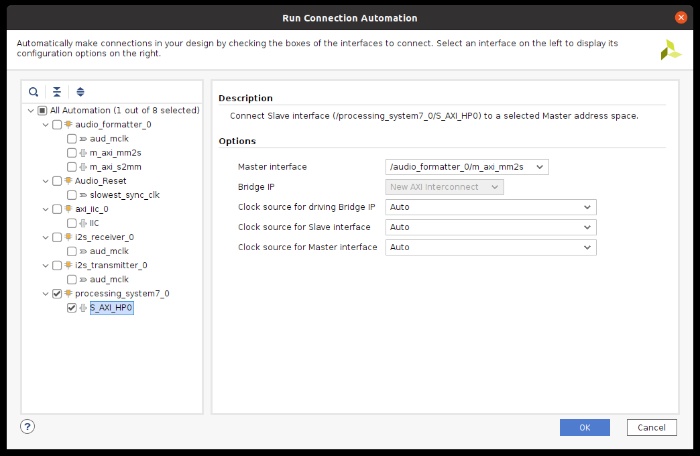

Diagram上部に出ている Run Connect Automation を実行し

- 接続対象に processing_system7_0 の S_AXI_HP0 を選ぶ

- S_AXI_HP0 の Master Interface には /audio_formatter_0/m_axi_mm2s を選択

としてから自動接続を行います。

Interrupts(クリックで拡大)

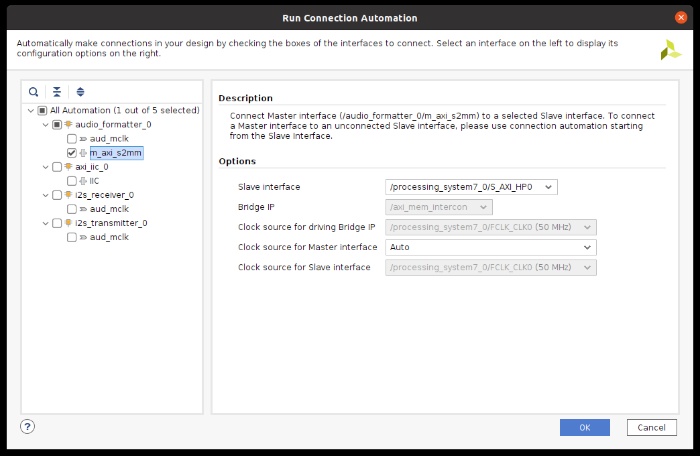

もう一度 Run Connect Automation を実行し

- 接続対象に audio_formatter_0 の m_axi_s2mm を選ぶ

- Saster Interface には /processing_system7_0/S_AXI_HP0 を選択

としてから自動接続を行います。

Interrupts(クリックで拡大)

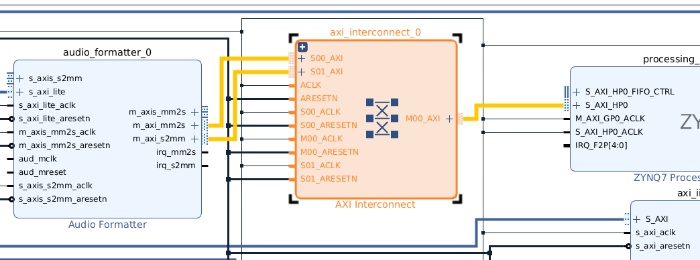

Inter Connect の接続部分

Inter Connect の接続部分(クリックで拡大)

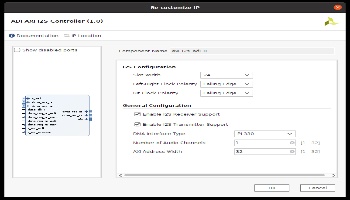

Xilinx IP の設定

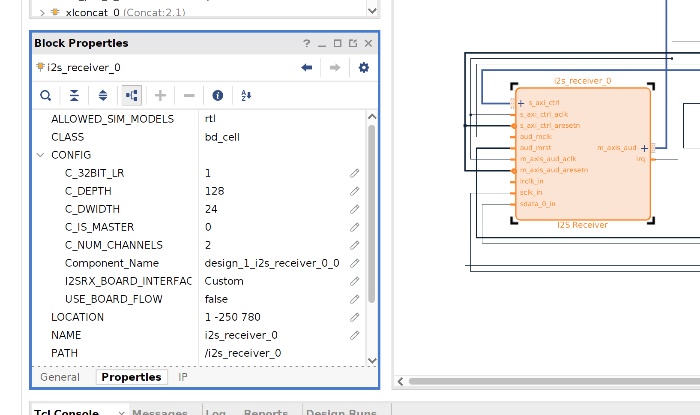

下記の通り、各IPの設定を変更します。

| IP | Paramater | Value | Remarks |

|---|---|---|---|

| I2S Transmitter | C_32BIT_LR | 1 | |

| I2S Reciever | C_32BIT_LR | 1 | |

| I2S Receiver | C_IS_MASTER | 0 | |

| AXI IIC | C_DEFAULT_VALUE | 0x01 | CodecのMute端子に割り当てる |

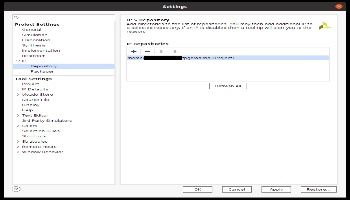

IPの設定は、IPを選択後、 Block Properties (初期設定ままだと画面左側に出る) のペイン下部の Propertiesタブを選ぶと変更できます。

I2S Receiver config例(クリックで拡大)

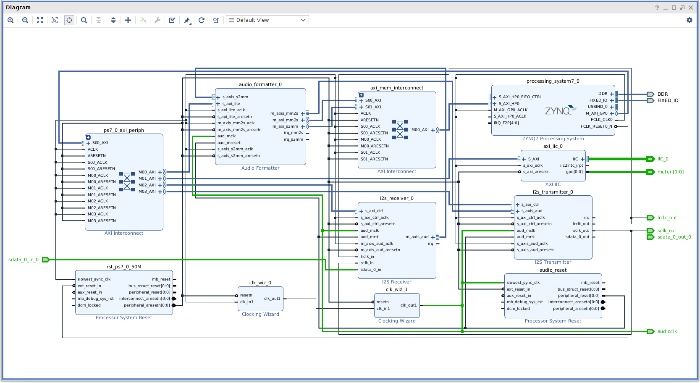

未接続部分を結線していく

まだIP間で接続が必要な箇所を、下図の通り接続していきます。

間違って接続した場合、 undo 機能(Ctrl+Zか、"戻る"アイコン)で戻るか、ピンを右クリック後 Disconnect Pin を選択すると、その接続のみ切断できるので、利用していきましょう。

ここまでのブロックデザイン(クリックで拡大)

外部入出力の追加と接続

外部入出力の作成と接続をします。

次のブロックデザインを元に、各IPの入出力信号から External Port / External Interface に接続します。

- 未接続なピンは、ピンを右クリックしたメニューから ”Make External" を選択します。

- 既に他と接続済みのピンは、ピン自体を右クリックして "Create Port" を選択します。

接続する外部ポート, Interface 一覧

| Port / Interface | 外部Port / Interfaceの名前 | 接続方向(Direction) |

|---|---|---|

| axi_iic_0:gpo[0:0] | muten[0:0] | Output |

| i2s_transmitter_0:lrclk_out | lrclk_out | Output |

| i2s_transmitter_0:sclk_out | sclk_out | Output |

| i2s_transmitter_0:sdata_0_out | sdata_0_out_0 | Output |

| clk_wiz_1:clk_out1 | audioclk | Output |

| i2s_receiver_0:sdata_0_in | sdata_0_in_0 | Input |

| IIC | IIC_0 | Mode:Master |

ブロックデザイン結果(クリックで拡大)

また、各Port/Interface の割当を示す制約ファイル xdc を、 PROJECT MANAGER →Add Sources から追加しておきます。

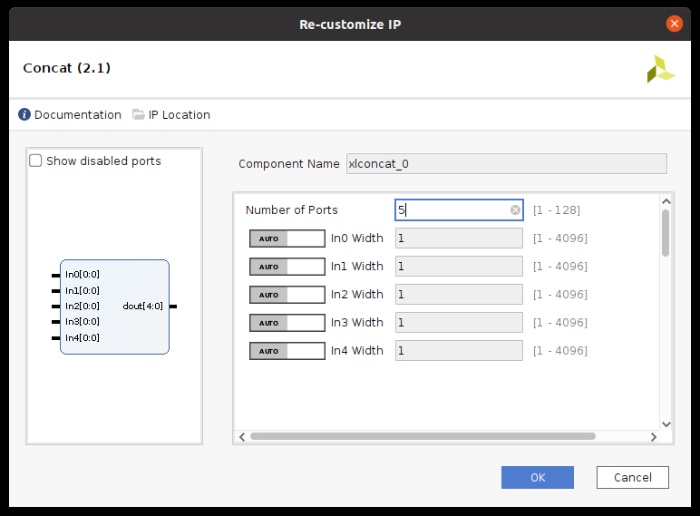

割込信号の接続

最後に、各IPの出力に設けられている割込み通知を、Zynqの割込入力に繋げます。一括して入力させるため、IP Concat で結合してから接続します。

今回は入力側信号が5つ必要なので、ポート数を変更します。

concatポート数(クリックで拡大)

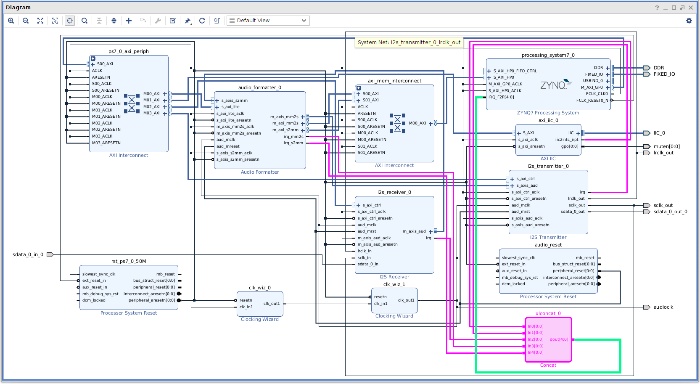

後は、次のブロックデザインを参照しながら、漏れがないように割込信号と入出力ポートを接続していきます。

ブロックデザイン結果(クリックで拡大)

これでようやくブロックデザインが完成です。

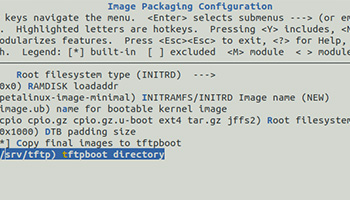

あとは、

- Create HDL Wrapper を実行

- Genarate Bitstream を実行

- File > Export > Export Hardware > Include bitstream

で xsa ファイルを作成しておきます。

※文中に記載されている各種名称、会社名、商品名などは各社の商標もしくは登録商標です。